Gegenstand der Förderung sind FuE-Aufwendungen in industrie- oder wissenschaftsgetriebenen vorwettbewerblichen Verbundvorhaben. Die geplanten Arbeiten müssen in mindestens einem der folgenden Bereiche den Stand der Technik deutlich übertreffen. Idealerweise und sofern möglich soll eine durchgängige parallele Hardware-Entwicklung vom Design bis zum fertigen Chip demonstriert werden.

a) Quelloffene EDA-Werkzeuge, PDKs und IP-Bibliotheken zur Vervollständigung und Stärkung der Werkzeugkette, bspw.:

Entwicklung quelloffener oder technologieoffener EDA-Werkzeuge und Werkzeugkomponenten einschließlich Entwurfs-, Simulations- und Verifikationswerkzeuge,

b) Entwicklung neuer (quelloffener) Entwurfsmethodik, bspw.:

Entwicklung von domänenspezifischen Hardware-Beschreibungssprachen und Werkzeugen zur HDL(hardware description language)-basierten Schaltungssynthese,

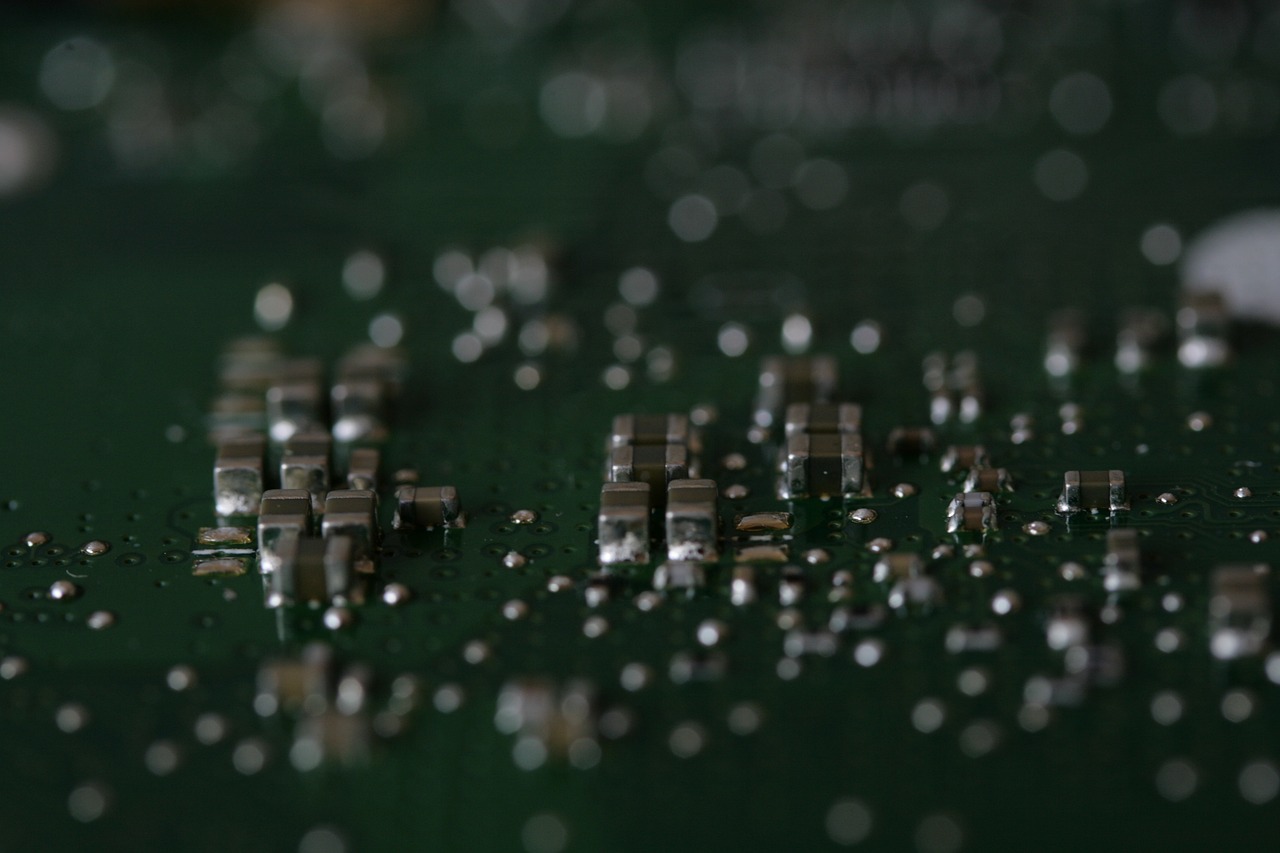

c) Neuartige Chipdesigns einschließlich neuer Ansätze für Architekturen und Topologien auf der Basis von quelloffenen EDA-Werkzeugen, PDKs und IP im Rahmen von Designprojekten mit der Erbringung des Nachweises der Machbarkeit in Form eines klassischen Hardware-Demonstrators oder eines virtuellen Demonstrators mit Elektronikhardware-Bezug

d) Entwicklung und Erforschung von Entwurfswerkzeugen, PDKs und IP für neuartige Technologien (z. B. Chiplets, Advanced Packaging, MEMS, Hochfrequenz, Hochvolt, (Ultra-) Low-Power, Photonik etc.). Neben quelloffenen Ansätzen sind auch Lösungen unter Nutzung von nicht quelloffenen (closed-source) Entwurfswerkzeugen und -methoden zugelassen, mit dem Ziel einer wirtschaftlichen Verwertungsperspektive für die Entwurfswerkzeuge selbst.

Bei der Planung der Vorhaben sollen zudem die folgenden Aspekte berücksichtigt und adressiert werden:

- Technologiesouveränität im Schaltungs- bzw. Systementwurf,

- Vertrauenswürdigkeit durch transparente und nachvollziehbare Designprozesse,

- die Einbeziehung der gesamten Entwicklungs- und Prozesskette bis hin zur Anwendung sowie

- Anforderungen an eine mögliche Standardisierung und Normung.

So sollen vorab klare Bezüge zur Technologiesouveränität und Vertrauenswürdigkeit im Chipdesign und in der Chipentwicklung hergestellt und konkrete Anwendungsperspektiven und Verwertungspotenziale identifiziert werden.

Antragsteller:

Unternehmen, Hochschulen und Forschungseinrichtungen

Förderquote:

Unternehmen (abhängig von der Unternehmensgröße) bis zu 60 %

Hochschulen und Forschungseinrichtungen bis zu 100 %

Einreichungsfrist:

Zweistufiges Verfahren (Skizze und Antrag), bis zum 31. Juli 2023

Als langjähriger Fördermittelberater unterstützen wir Sie gerne Full Service bei der Beantragung der Fördergelder, insbesondere Zuschüsse. Sie benötigen weitere Informationen? Rufen Sie uns an unter 02103 – 789060 oder schreiben Sie uns über unser Kontaktformular unter: www.gewi.de/kontakt; wir unterstützen Sie gerne und freuen uns auf Ihre Nachricht.

Übrigens: viele weitere Förderinformationen finden Sie in unserer Förderdatenbank www.gewi.de/newscenter